Práctica #10

Nombre de la práctica : Construyendo un camino de datos- El latch SR y los bloques de memoria

Nombre: David Santiago Martínez Molina

Código: 20181005164

Asignatura: Fundamentos de circuitos digitales

Programa : Ingeniería Electrónica

Docente : César Andrey Perdomo Charry

INTRODUCCIÓN:

Durante este informe se mostrará el desarrollo de la práctica #10. Para esta práctica se nos requiere implementar el sumador/restador de 6 bits, realizado en la práctica 9 y añadiéndole un banco de memoria además de incorporar la visualización dinámica. Para el desarrollo de esta práctica fue necesario comprender que son los circuitos Biestables, cuáles hay, y cómo es su funcionamiento. Y para la visualización dinámica fue necesario utilizar el integrado 74LS185 (conversor de binario a bcd o bcd a binario).

Los dispositivos biestables se dividen en dos categorías: flipflops y latches. Los biestables poseen dos estados estables, denominados SET (activación) y RESET (desactivación), en los cuales se pueden mantener indefinidamente, lo que les hace muy útiles como dispositivos de almacenamiento.

Latches:

El latch (cerrojo) es un tipo de dispositivo de almacenamiento temporal de dos estados (biestable), que se suele agrupar en una categoría diferente a la de los flip-flops. Básicamente, los latches son similares a los flip-flops, ya que son también dispositivos de dos estados que pueden permanecer en cualquiera de sus dos estados gracias a su capacidad de realimentación, lo que consiste en conectar (realimentar) cada una de las salidas a la entrada opuesta. La diferencia principal entre ambos tipos de dispositivos está en el método empleado para cambiar de estado.

-Latch S-R:

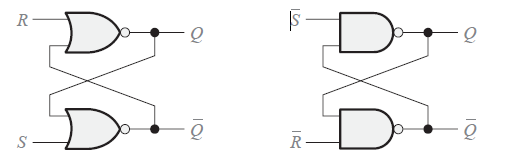

Un latch es un tipo de dispositivo lógico biestable o multivibrador. Un latch S-R (Set-Reset) con entrada activa a nivel ALTO se compone de dos puertas NOR acopladas; un latch con entrada activa a nivel BAJO está formado por dos puertas NAND. La salida de cada puerta se conecta a la entrada de la puerta opuesta. Esto origina la realimentación (feedback) regenerativa característica de todos los latches y flip-flops.

Figura 1.Latch S-R con entrada activa a nivel ALTO y BAJO.

Cuando las dos entradas,R y S, son iguales a cero, el latch mantiene su estado actual, que puede ser Q=0 y Q'=1, o Q=0 1 y Q'= 0. En este caso Q y Q' se complementan mutuamente. Cuando R=0 y S=1, el latch se fija en un estado donde Q=1 y Q'=0 (estado conocido como set). Cuando R=1 y S=0, el latch se regresa a un estado en el que Q=0 y Q'=1 (estado conocido como reset). La cuarta posibilidad es tener R=S=1. En este caso, tanto Q como Q' serán 0. Entonces el latch SR básico puede servir como un elemento de memoria útil, ya que recuerda su estado cuando las dos entradas S y R son 0.

-Latch S-R con habilitador:

Las entradas S y R controlan el estado al que va a cambiar el latch cuando se aplica un nivel ALTO a la entrada de habilitación (EN, enable). El latch no cambia de estado hasta que la entrada EN está a nivel ALTO pero, mientras que permanezca en este estado, la salida va a ser controlada por el estado de las entradas S y R.

Figura 2. Símbolo lógico.

MATERIALES Y EQUIPOS:

En el banco de memoria:

-7 entradas

-5 Mux 4 a 1(27 puertas NAND, 6 entradas, 1 salida)

-13 puertas NOT

-12 Flip-Flops SR

-12 salidas

Para el Mux 12 a 6:

-1 Mux 8 a 4

-1 Mux 4 a 2

-1 selector

Para el conversor de binario a BCD:

-Integrado 74LS185

Para la visualización dinámica:

-5 Integrados 74LS185

-7 decodificadores BCD a 7 segmentos implementados con compuertas NAND

METODOLOGÍA:

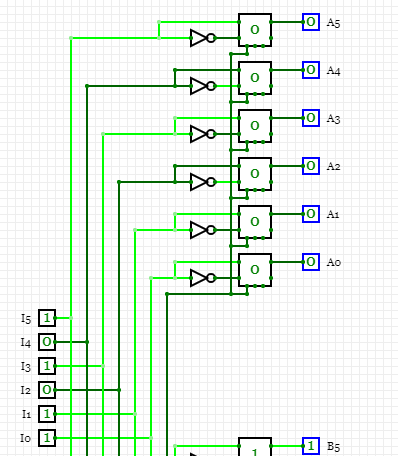

Como en la práctica anterior ya se había realizado el sumador/restador de 6 bits, entonces solo quedaría añadirle la visualización dinámica, y el banco de memoria. Para el banco de memoria se tiene que el circuito realizado contiene Flip-Flops SR, ya que nos permite la función de memoria, y queda de la siguiente manera:

Memoria para Dato A:

Memoria para Dato B:

Como se observa, la memoria realizada cuenta con una entrada donde se selecciona la entrada que se desea ingresar (A o B), y este dato queda guardado. Teniendo la memoria realizada y el correcto funcionamiento de la entrada de datos, tenemos que los datos ingresados ahora pasan al comparador de la siguiente manera:

Entonces teniendo en cuenta la salida del comparador, A< B, se tienen 2 Mux 12 a 6, en donde van los datos ingresados y dependiendo del valor que arroje el comparador se realiza el complemento de A o de B, así:

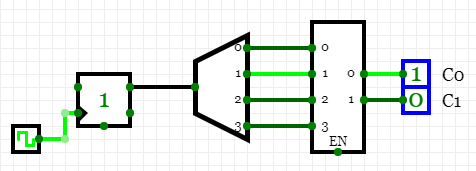

Cabe recordar que el complemento a 1 se activa únicamente si se tiene una resta. Ahora las salidas obtenidas del primer Mux y del segundo Mux, complementado o no, se dirigen al sumador de 6 bits, de la siguiente manera:

Como se puede observar se tienen 8 salidas, donde las salidas C0 a Cout, corresponden al resultado de la suma o resta, y la última salida que se encuentra a la izquierda, corresponde al signo del resultado. También se puede ver, que en la entrada Cin, se encuentra el selector, en donde elegimos si queremos realizar la suma o la resta, además que esta entrada nos permite hacer el complemento a 2 si se tiene una resta.

LINK DEL VÍDEO : https://youtu.be/mQmCYQ6thMs

ANÁLISIS DE RESULTADOS:

Ahora para realizar la visualización dinámica del resultado y de los datos ingresados, lo primero que se realizo fue el conversor de binario a BCD, teniendo en cuenta la hoja de datos del integrado 74LS185, en donde se encuentra la tabla de verdad del conversor de binario a BCD, y ya que el simulador nos genera un circuito ingresando la tabla de verdad, se pudo obtener el circuito correspondiente al conversor.

Teniendo esto, lo siguiente a realizar es el decodificador de BCD a 7 segmentos que va conectado al display 7. Entonces teniendo en cuenta que la tabla de verdad de este decodificador es:

Aplicando las leyes de DeMorgan para implementar el circuito únicamente con compuertas NAND, se tiene:

Y añadiéndole un habilitador para conectar el contador se tiene que el circuito realizado es:

Entonces para realizar la visualización dinámica se tiene que el contador que nos permite el efecto deseado. Entonces el contador es el siguiente:

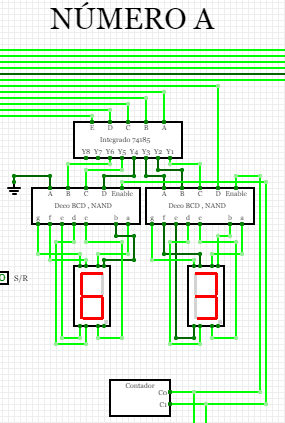

Con esto claro, para el dato A ingresado, la visualización dinámica se realizó de la siguiente manera:

En donde al integrado 74185 llegan los datos de A procedentes del banco de memoria, y la salida es en BCD, esta salida pasa por los decodificadores y como resultado se obtiene la visualización en los decodificadores. También se observa que el contador con una señal de reloj es el que habilita y des-habilita los decodificadores, con esto se percibe el efecto de visualización dinámica.

Y para el dato B la visualización dinámica es:

Ahora para implementar la visualización dinámica al resultado obtenido del sumador/restador se tiene que dicho resultado es un número de 7 bits, por ende el número mayor en decimal corresponde a 127, esto quiere decir que se necesitan 3 displays y 3 decodificadores BCD a 7 segmentos. Dicho número de 7 bits, tiene que convertirse a BCD para poder ingresarlo al decodificador y observar el número en el display, entonces para este conversor se utilizan 2 integrados 74185, siguiendo la hoja de datos, de la siguiente manera:

Entonces con el conversor ya hecho, se tiene que la visualización quedaría de la siguiente manera:

Y como se observa cada decodificador tiene conectada su respectiva entrada ENABLE al contador para poder observar el efecto de visualización dinámica. En el primer display de la izquierda se puede observar las centenas del resultado, pero también se puede observar el signo, de pendiendo si se esta realizando una resta, y si A< B.

Entonces el circuito total obtenido es:

En el anterior circuito, se pueden observar todos los circuitos desarrollados y se puede comprobar el funcionamiento del sumador/restador, además de poder visualizar la visualización dinámica.

CONCLUSIONES:

-Realizando el banco de memoria, se pudo profundizar más el tema de Biestables y una nueva etapa que son los circuitos secuenciales, haciendo un énfasis en el latch SR.

FUENTES:

- Floyd, T. (2006). Fundamentos de Sistemas Digitales (9.a ed., Vol. 1). Madrid, España: PEARSON EDUCACIÓN.

-Hoja de datos integrado 74185: https://pdf1.alldatasheet.es/datasheet-pdf/view/98237/TI/74185.html

-Brown, S. (2006). Fundamentos de Lógica Digital con Diseño VHDL (Segunda ed., Vol. 1). México, D. F., México: McGraw-Hill Companies.