Práctica #19

Nombre de la práctica : Contador de dos Dígitos ascendente-descendente

Nombre: David Santiago Martínez Molina

Código: 20181005164

Asignatura: Fundamentos de circuitos digitales

Programa : Ingeniería Electrónica

Docente : César Andrey Perdomo Charry

INTRODUCCIÓN:

En el presente informe se mostrará el desarrollo de la práctica #19. Para esta práctica tenemos un contador de dos dígitos ascendente y descendente. A dicho contador se le podrán ingresar sus respectivos límites superior e inferior, que son muy importantes a la hora de realizar el conteo. A lo largo de este informe se evidenciará la manera en que se implemento dicho contador y además se explicarán los componentes utilizados para su correcto funcionamiento.

MATERIALES Y EQUIPOS:

-Psoc 5LP

-Computador con Psoc Creator

-Tarjeta desarrolladora.

-Cables con conectores.

-Barra de Leds

-Pulsador.

METODOLOGÍA:

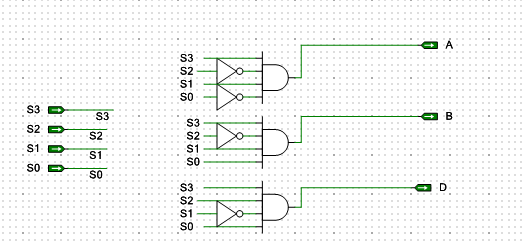

Para habilitar cada banco es necesario crear un identificador de las teclas A, B y D, ya que al presionar la tecla A se podrá ingresar el límite inferior y después de esto se presiona la tecla B y se ingresa el límite superior y posteriormente se presiona la tecla D para confirmar ambos datos y empezar el conteo. Por ende se tiene:

Y para que se puedan activar dichos bancos de memoria, se realiza a través de 2 flip-flop SR, que me habilitan y des-habilitan cada banco dependiendo la tecla que se presione, por ende se tiene:

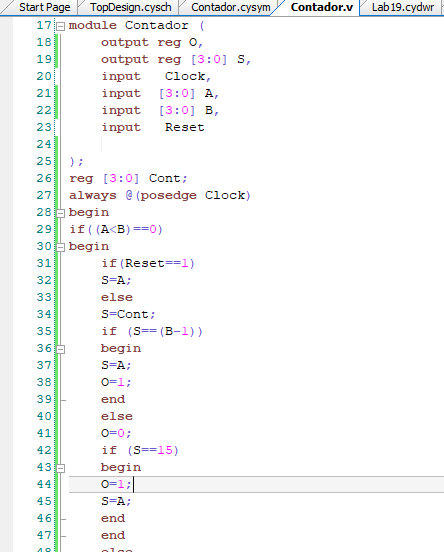

De esta manera ya se tienen ambos límites en cada banco de memoria, ahora lo que procede es realizar el contador. El contador mencionado será realizado en verilog, ya que puede ser una mejor opción en cuestión de espacio. El código realizado queda de la siguiente manera:

Y el símbolo del componente queda así:

Como tenemos un contador de 2 dígitos, por ende es necesario conectar dos contadores para obtener el resultado deseado. De esta manera la salida O, me va a indicar cuando el primer contador llegué a su límite máximo, que fue definido anteriormente. También se observa en el código, que dependiendo de si los límites ingresados son mayores o menores el uno al otro, se tiene el conteo ascendente o descendente. Entonces tenemos que la unión de los contadores queda:

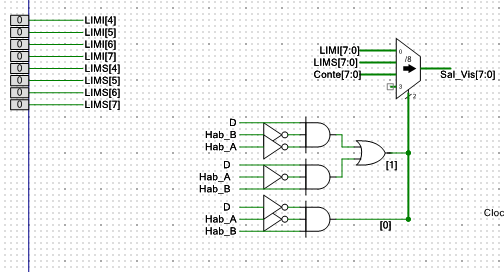

De esta manera ya se tiene el contador. Ahora queda realizar la visualización dinámica del dígito ingresado en ambos bancos y el respectivo conteo. Para esto se utiliza primeramente un Mux 4 a 1, donde cada entrada es un bus de 8 bits, ya que nuestro contador tiene una salida de 8 bits. Como se tienen 2 selectores, se necesita tener un circuito con compuertas en el cual se tengan los respectivos valores de dichos selectores, dependiendo lo que se tenga que visualizar. Por ende el multiplexor y el circuito que controla los selectores corresponde:

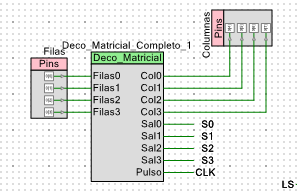

Ahora para la parte de visualización dinámica, se utiliza otro Mux de 4 a 1, donde cada entrada es de 4 bits. Los selectores de este mux son las salidas de un contador de 2 bits, que a su vez van conectados a un deco 2 a 4, que me permite poner en 0 los comunes de los displays 7 segmentos, como ya se venía trabajando anteriormente. La salida del Mux va conectada al respectivo decodificador BCD a 7 segmentos. Entonces la implementación de visualización dinámica queda:

ANÁLISIS DE RESULTADOS:

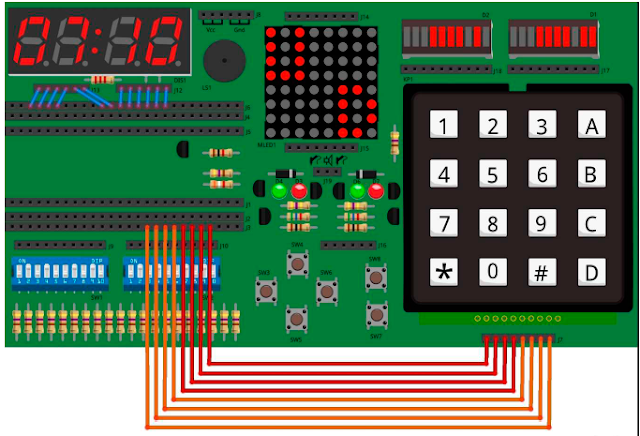

Con todo lo anterior, el respectivo montaje en la placa desarrolladora corresponde a:

CONCLUSIONES:

-Al implementar los contadores en verilog, se puede observar que si consume menos espacio que si se hubieran realizado mediante compuertas, también se pudo aprender más como se implementan circuitos mediante este lenguaje, describiendo su comportamiento.

FUENTES:

- Simulador utilizado : Psoc 5LP.- Floyd, T. (2006). Fundamentos de Sistemas Digitales (9.a ed., Vol. 1). Madrid, España: PEARSON EDUCACIÓN.