Práctica #14.

Nombre de la práctica : Sumador/Restador BCD ingresado por teclado matricial (1 dígito).

Nombre: David Santiago Martínez Molina

Código: 20181005164

Asignatura: Fundamentos de circuitos digitales

Programa : Ingeniería Electrónica

Docente : César Andrey Perdomo Charry

INTRODUCCIÓN:

A lo largo de este informe se mostrará el desarrollo de la práctica #14. El objetivo de esta práctica es implementar un Sumador/Restador de dos números BCD de un dígito, que serán ingresados por un teclado matricial en Psoc 5LP. Igualmente se utilizará la visualización dinámica en los displays 7 segmentos para visualizar el resultado de la suma o resta, y los números A y B ingresados. Para esta práctica fue importante utilizar algunos componentes de prácticas anteriores que fueron modificados según la conveniencia.

MATERIALES Y EQUIPOS:

-Psoc 5LP

-Computador con Psoc Creator

-Tarjeta desarrolladora.

-Cables con conectores.

-Teclado Matricial.

-Display 7 segmentos.

METODOLOGÍA:

Primeramente para desarrollar este laboratorio, implementamos el decodificador de teclado matricial, realizado en la práctica #11. Dicho decodificador es el siguiente:

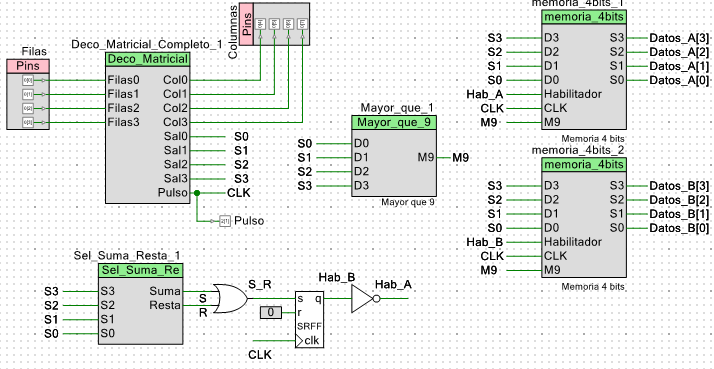

Cabe recordar que a las salidas de este decodificador se encuentra una salida denominada "Led", esta salida es el pulso que se genera al presionar cualquier tecla del teclado, que va a ser muy importante más adelante. Para las otras salidas se tiene que crear un decodificador que me genere la conversión a binario natural, dicho decodificador fue implementado por el LUT del simulador. Entonces el decodificador de teclado matricial completo esta compuesto por el LUT y el circuito mostrado anteriormente, de la siguiente manera:

Con el decodificador de teclado matricial completo, ahora lo siguiente es diseñar el banco de memoria de los números A y B ingresados. Para este banco de memoria, lo diseñe utilizando Flip-Flops tipo D, y Multiplexores 2 a 1. Se tiene que tener en cuenta que un banco de memoria o registro, me permite dos funciones: Lectura y Escritura. La escritura es que me permita ingresar un dato al banco y me lo guarde, mientras que la lectura me permite ver cuál es el dato guardado pero sin afectar este dato. Entonces según lo anterior, el multiplexor 2 a 1 me va a permitir ingresar el dato(Escritura), o visualizar el dato sin cambiarlo (Lectura), teniendo en cuenta que para poder visualizar este dato se conecta la salida Q del Flip-Flop a una entrada del Mux. Entonces el banco de memoria de 4 bits queda de la siguiente manera:

Como se observa en el circuito anterior, se tienen 7 entradas, 4 corresponden a los datos a guardar (D0,D1...D3), las otras 3 son : el habilitador, un clock(CLK) y M9. La entrada habilitador es la que va a comportarse como el selector de los Mux 2 a 1 y me permitirá ingresar el dato cuando se encuentre en 1 y tener el dato sin modificarlo cuando se encuentre en 0. Las entradas CLK y M9 son las entradas de una puerta AND que a su salida va conectada a los clocks de cada Flip-Flop. Esto se realiza ya que como lo mencione al inicio el sumador/restador es de dos números BCD, entonces se tiene que buscar una manera de que si se ingresa un número no BCD, o sea mayor que 9, el banco de memoria no me tome este dato y me des-habilite estas entradas, y mediante una puerta AND en donde sus entradas son un comparador que me permita saber cuando el dato ingresado sea mayor que 9 y un clock, se logra hablitar o des-habilitar el ingreso de datos al Flip-Flop. Entonces la entrada M9 corresponde a la salida A<9 de un comparador de 4 bits. La entrada CLK corresponde a un clock, que en este caso utilicé el pulso que se genera al oprimir cualquier tecla del teclado matricial. De esta manera si se ingresa un dígito mayor a 9 se genera un 1 en M9 y mediante una puerta NOT este dato pasa a ser 0 y con la puerta AND me des-habilita el CLK y no se guardará ni modificará el dato del registro.

De esta manera se realizaron los bancos de memoria para A y para B,y el resultado es el siguiente:

Ahora lo que prosigue es poder habilitar cada banco. Teniendo en cuenta las instrucciones dadas por el docente, el inicio del modo de operación de nuestro circuito tiene que ser:

-Inicialmente el sistema tiene habilitado el ingreso de A el cual debe ser un numero entre 0-9. Durante este paso se debe visualizar el dato A en el display.

-Luego de ingresado se debe presionar * para suma o # para resta, al hacer esto se confirma el dato A y se habilita el banco de memoria B.

Esto quiere decir que el banco de memoria B se habilita si se presiona * o #, y el banco de memoria A esta habilitado a penas se inicie el sistema. Entonces para poder habilitar estos bancos hay que hacer un detector de cuando se presione * o #, que a su vez me indican si se va a realizar una suma o una resta. Para ello se realizo el siguiente circuito que me permite detectar cuando se oprime * o # (teniendo en cuenta el número binario asociado a estas teclas, que son 1110 para * y 1111 para #):

Al presionar cualquiera de estas teclas se tiene que habilitar el banco de memoria B y confirmar el dato ingresado al banco de memoria A, por ende se realiza lo siguiente:

En la anterior imagen se observa que las salidas del detector de código realizado anteriormente son las entradas de una puerta OR, que es la que me permite saber si se oprimió alguna de las dos teclas. La salida de esta puerta OR va conectada a la entrada S de un Flip-Flop tipo SR, y tiene su entrada R en 0 en todo momento, y la salida es la que me va a permitir habilitar el banco de memoria B y con una compuerta NOT, habilitar el banco A.

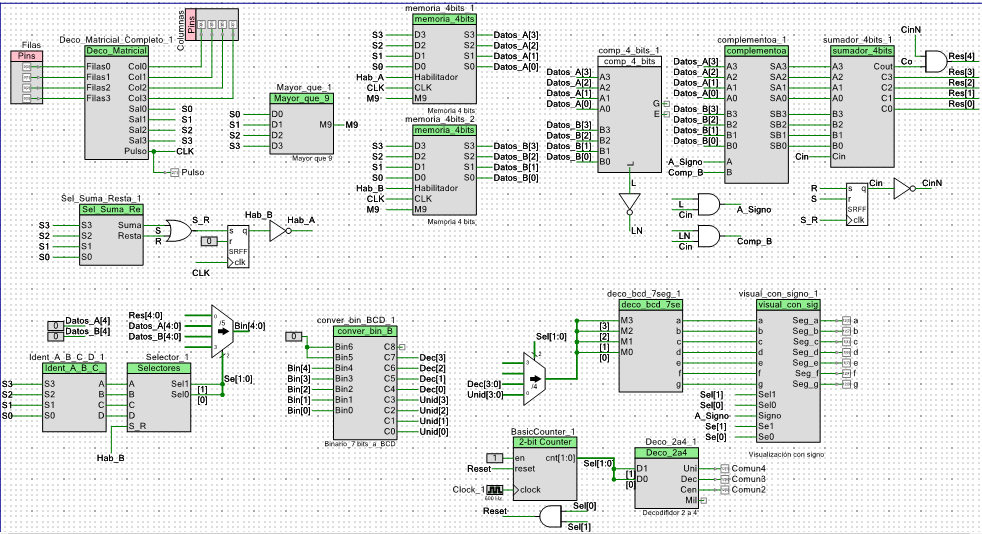

De esta manera el circuito con el banco de memoria, el decodificador de teclado matricial, el comparador de mayor a 9 y los habilitadores de los bancos es:

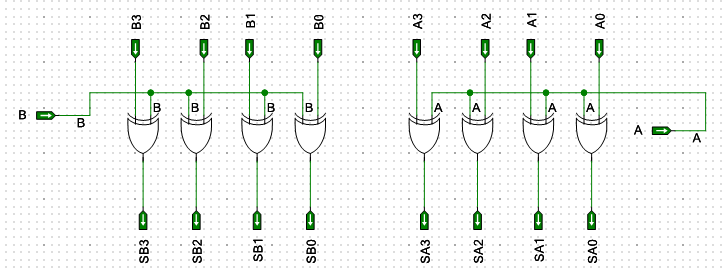

Lo siguiente a realizar es el sumador/restador, con los datos de los bancos de memoria. Pero primero se tiene que tener en cuenta que la resta igual que en prácticas anteriores, se realizará por complemento a 2, por ende es necesario tener un comparador de 4 bits que me indique cuando A< B y con esto se realiza el complemento según sea el caso. Este comparador fue realizado a partir de comparadores de 2 bits explicados en prácticas anteriores. Teniendo en cuenta la salida del comparador, se realiza el bloque de complemento a 1 de 4 bits, de la siguiente manera:

Teniendo en cuenta que las entradas A y B dependen de la salida del comparador y si se tiene una suma o una resta. Esta explicación se encuentra más detallada en la práctica #12 (Ver práctica #12). Con esta parte realizada, ahora si se plantea el sumador. Este sumador puede realizarse como un sumador BCD o un sumador de 4 bits binario y realizar la conversión del resultado a BCD. Para este caso implementare la segunda opción. Entonces el sumador de 4 bits fue realizado a partir de 2 sumadores de 2 bits, conectados en cascada, de la siguiente manera:

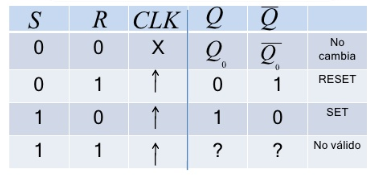

Con el sumador realizado, y siguiendo con la implementación de la resta, se tiene que el complemento a 2 se realiza mediante el bit que se añade en el Cin del primer sumador, que a su vez es el selector de suma o resta. Como mencione anteriormente, la suma se va a realizar cuando se oprime la tecla *, y la resta se va a realizar cuando se oprime la tecla #. Esto quiere decir que cuando se oprime * se tiene un 0 en el Cin, y cuando se oprime # se tiene un 1 en Cin. Para lograr esto lo realice con un Flip- Flop SR, en donde la entrada R va conectada a la salida Suma del componente Selector_Suma_Resta mostrado anteriormente y la entrada S va conectada a la salida Resta del componente mencionado, y en el clock va la salida de la puerta OR cuando se presiona cualquier tecla, teniendo en cuenta que el funcionamiento de un Flip-Flop SR es de la siguiente manera:

De esta manera ya se tiene cuando va a realizarse una suma o una resta. Entonces para el signo cuando se realiza una resta, se tiene que tener en cuenta Cin y la salida del comparador, o sea si A<B y con esto se sabe si es positivo o negativo, utilizando una puerta AND. Para la corrección del bit de más generado al hacer una resta, también se realiza con una puerta AND en donde sus entradas van a ser el Cout del sumador y la negación de Cin. Entonces el circuito del SUMADOR/RESTADOR de dos números BCD queda de la siguiente manera:

Visualización dinámica:

Para la implementación de la visualización en los displays 7 segmentos, se tiene que según las indicaciones del docente, al ingresar el dato del banco de memoria A este se tiene que visualizar en el display, al oprimir la operación que se desea, se confirma el dato A y se prosigue a introducir el dato del banco de memoria B. Dicho dato también se debe visualizar en el display. Si se presiona la tecla D se tiene que visualizar el resultado o sea funciona como un igual. Si se presiona A se visualiza A, si se presiona B se visualiza B, y por último si se presiona C se visualiza el resultado.

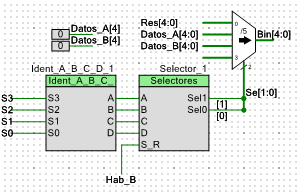

Entonces para poder realizar esto utilicé un Mux de 4 a 1, pero en cada entrada va un bus de 5 bits, o sea en realidad se tiene un Mux de 20 a 5, con dos selectores. Para la primera entrada de este Mux (00) se tienen los datos de la respuesta de la suma o resta, en la segunda entrada (01) se tienen los datos del registro A, en la tercera entrada (10) se tienen los datos del registro B.

Pero según las indicaciones ya mencionadas, al presionar las teclas A o B o C o D se tiene que visualizar su correspondiente. Para lograr esto, primero se hace un detector de código, que me detecte las teclas mencionadas, teniendo en cuenta su correspondiente en la salida del teclado matricial (A=1010, B=1011, C=1100, D=1101), entonces se realiza de la siguiente manera:

Con este detector, ahora se tiene que realizar el respectivo componente que dependiendo las combinaciones que se tengan o de las teclas que se opriman, a la salida se tenga la respectiva combinación que va a los selectores y por ende sea visualizada. Para esto se plantea una tabla de verdad (Tabla de verdad selectores) teniendo en cuenta las entradas A, B, C, D y a parte el habilitador del banco B, para mostrar este dato en el display cuando se termine de ingresar el dato A y se elija la operación deseada. Y para obtener la ecuación de salida de cada salida, se realizan mapas de Karnaugh y se obtienen las siguientes ecuaciones de salida:

Entonces de esta manera se manejan los selectores del Mux, dependiendo de la tecla que se oprima y a la salida se tiene el dato que se quiera visualizar. Por ende el circuito completo para esta parte queda de esta manera:

Ahora las salida de este Mux van un conversor de binario a BCD, ya que como lo mencione anteriormente, no implemente el sumador BCD y por ende el resultado es un número binario de 5 bits, entonces para realizar esta conversión utilizamos el integrado 74185, que fue implementado en la práctica anterior y ya se tiene como un componente. Entonces se tiene lo siguiente:

Las salidas C0 a C3, corresponden a las unidades, las salidas C4 a C7 a las decenas y la salida C8 corresponde al bit menos significativo de las centenas. En este punto ya se tiene el número en BCD ahora para implementar la visualización dinámica la realizare con un contador de dos bits, que se encuentra en Psoc como BasicCounter, que va tener un 1 en la entrada enable y para el Reset se va a tener en cuenta las salidas y con una compuerta AND se logrará que el contador llegué a los bits 10 y después se resetee. También sus salidas van conectadas a un decodificador 2 a 4, que me permitirá poner en 0 los pines comunes para cada display, que corresponden a Unidades, Decenas y Centenas ya que se tienen 4 displays de cátodo común. Para poder percibir de una mejor manera la visualización dinámica el clock implementado tiene una frecuencia de 600Hz, y esto nos permite que el ojo humano no sea capaz de percibir el cambio. Entonces el circuito implementado es:

Y el circuito del decodificador:

Ahora para pasar los datos de las unidades,decenas, y centenas a los displays, es necesario realizar un Mux de 16 a 1, para esto igual que antes, se utiliza un Mux 4 a 1 poniendo en cada entrada un bus de 4 bits. Los selectores de este Mux van conectados con las salidas del contador mencionado anteriormente. Teniendo en cuenta esto, las salidas del Mux van conectadas a un decodificador de BCD a 7 segmentos y ya se tiene la visualización dinámica deseada. De esta manera el circuito para realizar la visualización en los displays queda así:

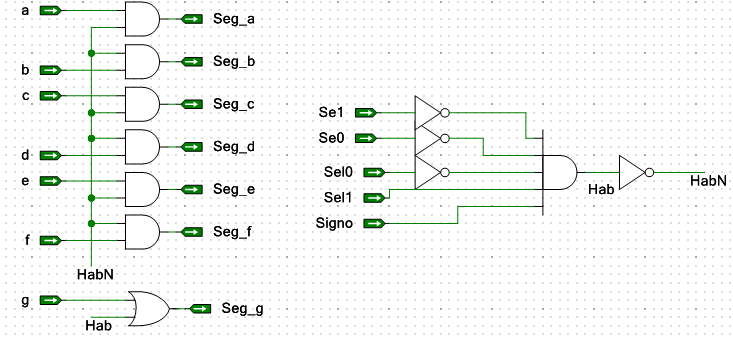

Hay que tener en cuenta que en la visualización también se tiene que poder ver el signo del resultado cuando es una resta y el número A es menor que el número B. En la imagen anterior se puede ver que se encuentra un componente adicional conectado a las salidas del decodificador BCD a 7 segmentos, este componente es el que me permite visualizar el resultado, el número A, y el número B con su signo correspondiente. Para realizar este componente, hay que tener en cuenta que cuando algún número es negativo se deben des-habilitar las salidas de los segmentos, excepto la salida del segmento g, ya que este es el que permite visualizar el signo - . Analizando esto, el caso donde únicamente se mostraría el signo sería el siguiente:

Teniendo en cuenta que los selectores de visualización (Se1 y Se0) cuando están en 00, se tiene que visualizar el resultado y que las salidas del contador (Sel1 y Sel0), que a su vez son los selectores del Mux, cuando están en 10 se tienen las centenas y en ese display es donde se requiere que se visualice el signo según corresponda. Cabe recordar que también hay que des-habilitar los otros segmentos y solo se tiene activo el segmento g. Esto se realiza con compuertas AND y colocando una entrada común que va a ir a la función de SALIDA negada. Quiere decir que cuando SALIDA sea 1, o sea se visualiza el signo, los segmentos del a al f serán des-habilitados.

Implementando el circuito se tiene:

Finalmente, ya se obtiene la visualización dinámica del resultado, número A y número B, con el respectivo signo, según la operación. Por ende, el circuito total del SUMADOR/RESTADOR de dos números BCD ingresado por teclado matricial con visualización dinámica es:

ANÁLISIS DE RESULTADOS:

Con el circuito ya realizado en Psoc, ahora solo queda comprobar su funcionamiento, utilizando la tarjeta desarrolladora. Por ende las conexiones necesarias para probar este circuito requeridas por el docente son:

Siguiendo este montaje, las conexiones realizadas en la tarjeta desarrolladora quedan de la siguiente manera:

Entonces con el montaje ya realizado y con las conexiones adecuadas, en el siguiente vídeo se muestra su funcionamiento:

CONCLUSIONES:

-Al comprobar el funcionamiento del sumador/restador BCD ingresado por teclado matricial de 1 solo dígito en la placa desarrolladora, se puede ver que funciona correctamente y se visualiza el resultado, el número A y el número B ingresados, cumpliendo con las instrucciones dadas por el docente para su operación.

-Después de ejecutar el programa, se pudo ver los recursos utilizados de UDB son:

Macrocells: 39.98%

Unique P-terms: 59.64%

FUENTES:

- Simulador utilizado : Psoc 5LP.-Hoja de datos integrado 74185: https://pdf1.alldatasheet.es/datasheet-pdf/view/98237/TI/74185.html