Práctica #7.

Nombre de la práctica : Visualización dinámica, el sumador BCD

Nombre: David Santiago Martínez Molina

Código: 20181005164

Asignatura: Fundamentos de circuitos digitales

Programa : Ingeniería Electrónica

Docente : César Andrey Perdomo Charry

INTRODUCCIÓN:

A lo largo de este informe se mostrará el desarrollo de la práctica #7. En esta práctica se necesita realizar un sumador de dos números BCD y mostrar el resultado en dos displays 7 segmentos utilizando visualización dinámica para mostrar las decenas y unidades. Para realizar esta práctica se necesita tener claro que es un Multiplexor, un comparador y un decodificador. En el caso del decodificador ya lo hemos trabajado en prácticas anteriores, entonces esta perfectamente claro.

Decimos que un multiplexor (MUX) es un dispositivo que permite dirigir la información digital procedente de diversas fuentes a una única línea para ser transmitida a través de dicha línea a un destino común. El multiplexor básico posee varias líneas de entrada de datos y una única línea de salida. También posee entradas de selección de datos, que permiten conmutar los datos digitales provenientes de cualquier entrada hacia la línea de salida. A los multiplexores también se les conoce como selectores de datos.

Los multiplexores más grandes también pueden construirse a partir de otros más pequeños. Por ejemplo, el multiplexor cuatro a uno puede construirse con tres multiplexores dos a uno.

La cantidad de entradas que se puede seleccionar depende de la cantidad de selectores en función de 2^n donde n es el número de selectores.

Un comparador consiste en comparar las magnitudes de dos cantidades binarias para determinar su relación. En su forma más sencilla, un circuito comparador determina si dos números son iguales. Además de disponer de una salida que indica si los dos números son iguales, muchos circuitos integrados comparadores tienen salidas adicionales que indican cuál de los dos números que se comparan es el mayor. Esto significa que existe una salida que indica cuándo el número A es mayor que el número B (A > B) y otra salida que indica cuándo A es menor que B (A < B).

MATERIALES Y EQUIPOS:

En el sumador de 4 bits se utilizaron los siguientes materiales:

-4 sumadores de 1 bit ( 1 puerta XOR de 3 entradas, 3 puertas NAND de 2 entradas, 1 puerta NAND de 3 entradas)

En el comparador de 5 bits:

- 1 comparador de 4 bits. ( construido a partir de 4 comparadores de 1 bit, 8 puertas AND de 2 entradas, 8 puertas NOT, 4 puertas XNOR de 2 entradas)

- 1 comparador de 1 bit.

- Circuito adicional (6 entradas, 4 puertas AND de 2 entradas, 1 puerta AND de 4 entradas, 2 puertas OR de 2 entradas, 3 salidas)

En el Multiplexor 8 a 4:

-2 Mux 4 a 2 ( construido a partr de 2 Mux 2 a 1, 2 puertas AND de 2 entradas,1 puerta NOT, 1 puerta OR)

-1 selector.

En el decodificador BCD a 7 segmentos:

-4 entradas.

-4 puertas NOT.

-15 puertas AND de 2 entradas.

-1 puerta AND de 3 entradas.

-3 puertas OR de 4 entradas.

-2 puertas OR de 3 entradas.

-1 puerta OR de 5 entradas.

-1 puerta OR de 2 entradas.

-7 salidas.

En el One hot y el circuito Enable:

- 1 puerta NOT.

-7 puertas AND de dos entradas.

Para el sumador BCD se utilizó:

- 2 sumadores de 4 bits.

- 1 comparador de 5 bits

- 1 Mux 8 a 4.

- 1 clock(Selector).

- 1 decodificador BCD a 7 segmentos.

- 1 one hot.

- 2 circuitos enable.

-2 Display de 7 segmentos.

METODOLOGÍA:

En el desarrollo de esta práctica, lo primero que realicé fue crear el decodificador BCD a 7 segmentos, entonces la tabla de verdad construida, teniendo en cuenta los leds del display que deben encender para ver el número en decimal, es la siguiente:

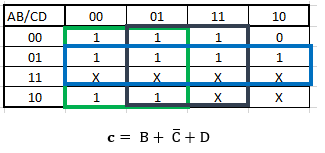

Y a partir de esta tabla de verdad, se obtuvieron los mintérminos correspondientes y se realizaron los Mapas de Karnaugh por cada salida, para obtener la ecuación de salida reducida y como resultado se obtuvo:

-Salida a:

-Salida d:

-Salida g:

Ahora lo siguiente que realice fue el comparador de 1 bit, para poder formar un comparador de 2 bits, y después uniendo dos comparadores de 2 bits obtener un comparador de 4 bits, entonces los circuitos correspondientes son:

Figura 3. Comparador de 1 bit.

Figura 4. Comparador de 2 bits.

Figura 5. Comparador de 4 bits.

El circuito que se observa en la figura 4 y 5, se realizo a partir de los mapas de Karnaugh, teniendo en cuenta las condiciones que no importan o que nunca se deben dar a las salidas de los comparadores, entonces para la salidas G (A>B), E(A=B), L(A<B), se tiene:

Para realizar el Multiplexor, se partió del Mux 2 a 1, que fue visto en clases, y con este multiplexor se pueden formar los otros multiplexores hasta llegar al que deseamos, teniendo en cuenta los selectores que se necesitan, entonces los circuitos realizados son:

Figura 6. Mux 2 a 1.

Figura 7. Mux 4 a 2.

En el siguiente vídeo se puede observar la metodología utilizada y una explicación del laboratorio realizado:

LINK DEL VÍDEO : https://youtu.be/2HJR_GR9BXk

ANÁLISIS DE RESULTADOS:

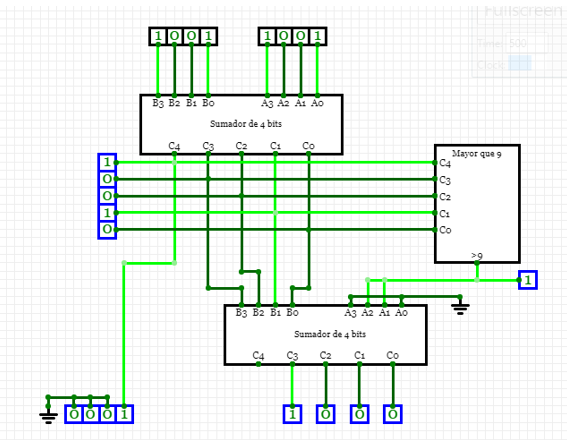

Teniendo en cuenta el comparador y el sumador de 4 bits (que habíamos realizado en una práctica anterior), se procedió a armar el sumador BCD, y como resultado se obtuvo

El comparador de 5 bits fue realizado, como se menciono anteriormente a partir de un comparador de 4 bits y añadiendo le 1 comparador de un bit, con el circuito mostrado anteriormente, entonces se realizó de la siguiente manera:

Cabe resaltar que este comparador fue diseñado para corregir el error de la suma BCD, ya que si el resultado de una suma BCD es mayor que 9, se tiene que sumar 6 para poder corregir el resultado y quede correctamente, entonces teniendo esto claro, el comparador que se realizo fue teniendo en cuenta que la salida de la suma se compara directamente con el número 9, y solo se desea saber si este número es mayor o no que 9. Por ende el circuito del comparador mayor que 9, queda de la siguiente manera:

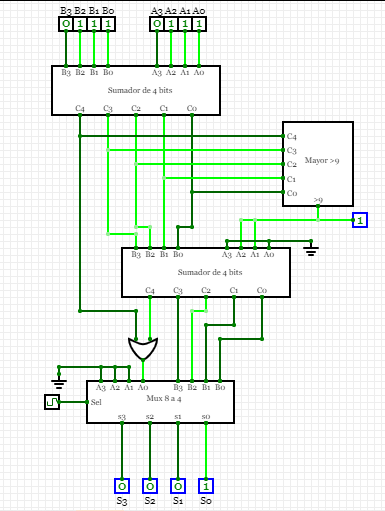

Ahora con la salida ya corregida, se utiliza el Mux 8 a 4 (que fue formado a partir de 2 Mux 4 a 2) y se implementa a nuestro sumador BCD para obtener en la salida las decenas o unidades, dependiendo del estado lógico del selector, que en este caso usamos como selector el elemento "clock" que nos proporciona el simulador CircuitVerse, y como resultado se obtiene:

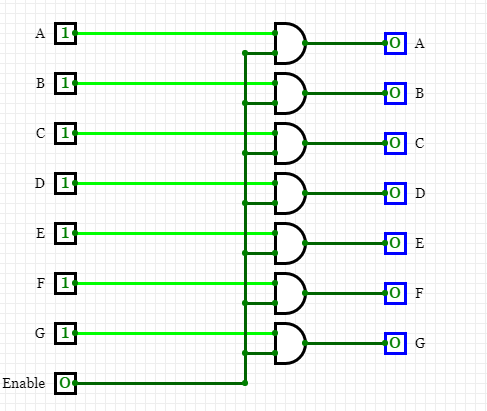

Lo siguiente a realizar es el circuito Enable, que nos permite tener la visualización dinámica, ya que en el simulador el display 7 segmentos no posee cátodo ni ánodo común entonces se utiliza este circuito para obtener lo desado. El circuito proporcionado por el docente es:

Ahora para activar o desactivar el enable, de acuerdo a la señal de reloj que tenemos, se utilizó un circuito One hot, que se realizo de la siguiente manera:

Este circuito nos permite habilitar y deshabilitar un enable para con esto poder ver en un display las decenas y en el otro las unidades, sin que los dos displays muestren lo mismo.

Entonces uniendo lo que mencionamos anteriormente, junto con el decodificador BCD a 7 segmentos, que va conectado a los circuitos Enable, se tiene finalmente como resultado el siguiente circuito :

En el anterior circuito se pueden ver cada uno de los circuitos realizados y verificarlos para ver el resultado obtenido de esta práctica, también se encuentra un circuito reducido donde se puede observar mejor el comportamiento, en la pestaña de "CIRCUITO COMPLETO".

CONCLUSIONES:

-La práctica se realizo de la mejor manera, y se pudo entender y aplicar el concepto de los multiplexores y comparadores, así como reforzar el conocimiento de los decodificadores.

-Nos podemos dar cuenta de que los circuitos enable solo se utilizaron en esta práctica y en este simulador, ya que el display que se maneja no posee cátodo ni ánodo común, entonces se requirió de este circuito para poder asimilar el efecto que se quiere lograr de visualización dinámica, entonces en la vida real estos circuitos no serían necesarios para producir este efecto.

FUENTES:

- Floyd, T. (2006). Fundamentos de Sistemas Digitales (9.a ed., Vol. 1). Madrid, España: PEARSON EDUCACIÓN.

-Brown, S. (2006). Fundamentos de Lógica Digital con Diseño VHDL (Segunda ed., Vol. 1). México, D. F., México: McGraw-Hill Companies.